Kioxia has prototyped a high-speed flash drive for edge servers with serially connected flash “beads” using the PCIe 6 bus.

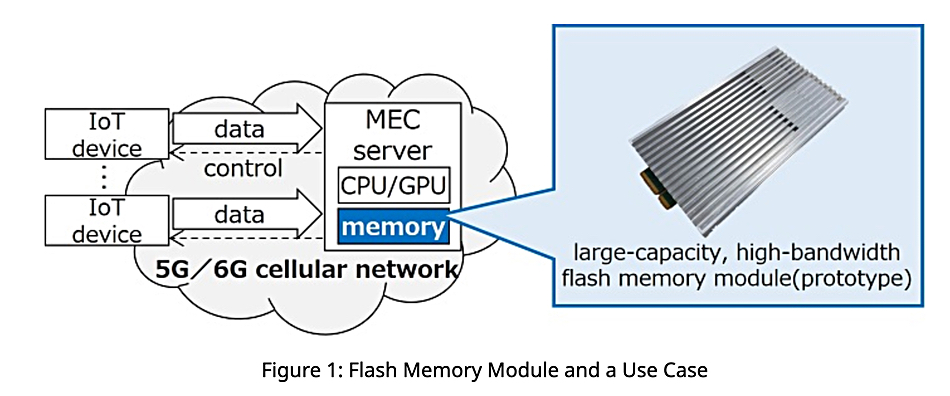

The edge servers are envisaged to be mobile edge units, connected by 5G or 6G cellular networks to IoT devices, and processing their inputs using AI models. They will have limited memory for the usual DRAM-is-expensive reason and so could augment the DRAM with flash, if the flash has high-enough bandwidth.

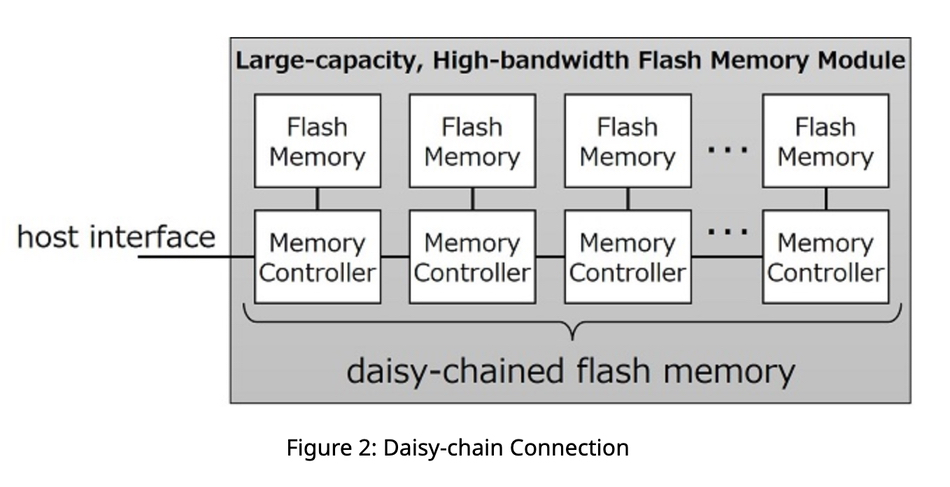

Kioxia has devised a method of increasing the bandwidth by using separate so-called “beads” of flash connected in a daisy-chain and using differential serial signalling, not parallel signalling, with two bits of data transmitted per signal and not one. It has built a prototype unit with 5 TB of capacity and a 64 GBps data rate when delivering data across a PCIe Gen 6 bus with eight lanes to a host server’s processors.

In comparison, a Micron 9650 Pro SSD has a PCIe Gen 6 x 4 lane link and a capacity range of 6.4 TB to 25.6 TB. It delivers up to 28 GBps sequential read and 14 GBps sequential write bandwidth. That’s 7 GBps per lane. The Kioxia HBF prototype delivers up to 64 GBps from its 5 TB capacity over the same PCIe Gen 6 bus, but with eight lanes. That’s about 2.3x the total throughput of Micron’s 9650 Pro, though only around 14 percent higher on a per-lane basis (8 GBps versus 7 GBps).

Kioxia’s high-bandwidth flash (HBF) has beads of flash and controllers connected in daisy-chain fashion to each memory board instead of a bus connection. It says that “bandwidth is not degraded even when the number of flash memories (beads) is increased.” The 2 bits per daisy-chain signal is achieved with PAM4 (4-level Pulse Amplitude Modulation) with four distinct voltage levels used to encode data, giving four possible 2-bit combinations; 00, 01, 10, and 11. PCIe 6 also uses PAM4 signalling.

The company has developed 128 Gbps PAM4 high-speed, low-power transceivers, and the prototype’s 64 GBps bandwidth needs less than 40 W of electricity. We understand Micron’s 9650 Pro has a peak power usage of 25 W during sequential read operations.

Kioxia says it has achieved 4 Gbps bandwidth between a memory bead and its controller “by applying low amplitude signalling and distortion correction/suppression technology to the interface.” Read latency has been shortened with controller pre-fetch technology used during sequential data accesses.

Sandisk, Kioxia’s NAND fab joint venture partner, also has HBF technology but implemented in a different way. The Sandisk HBF is a set of stacked NAND layers with connecting wires (Through-Silicon Vias or TSVs) linking each layer to a base interposer unit, which connects them to a host GPU in parallel, not serially.

Kioxia is looking to develop its HBF technology for mobile edge servers involved in IoT, big data analysis, and AI processing.